#### **Features**

- 5 V ±5% Power supply

- SLG55021 Drain Voltage Range 1.0 V to 20 V

- · Internal Gate Voltage Charge Pump

- · Controlled Turn on Delay

- · Controlled Load Discharge Rate

- · Controlled Turn on Slew Rate

- Stable Slew Rate (±2% typ) over Temperature Range

- TDFN-8 Package

- · Pb-Free / Halogen-Free / RoHS compliant

# **Applications**

- · Power Rail Switches

- · Hot Plugging Applications

- · Soft Switching

- · Personal computers and Servers

- · Data Communications Equipment

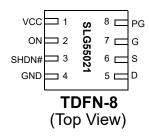

# **Pin Configuration**

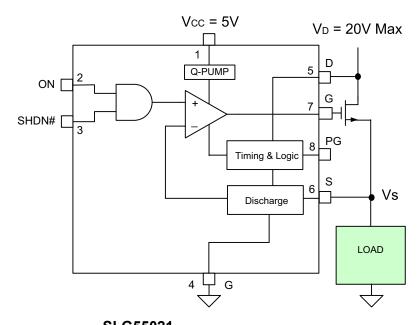

# **Block Diagram**

SLG55021 For N-MOSFETS with  $V_{GS} < 20V$

# **Pin Description**

| Pin#  | Pin Name | Type   | Pin Description                                                      |  |  |  |

|-------|----------|--------|----------------------------------------------------------------------|--|--|--|

| VCC   | 1        | Power  | Supply Voltage                                                       |  |  |  |

| ON    | 2        | Input  | IOS Logic Level. High True                                           |  |  |  |

| SHDN# | 3        | Input  | nut Down# - Low True Signal which immediately turns FET off          |  |  |  |

| GND   | 4        | GND    | Ground                                                               |  |  |  |

| D     | 5        | Input  | ET Drain Connection                                                  |  |  |  |

| S     | 6        | Input  | Source Connection                                                    |  |  |  |

| G     | 7        | Output | ET Gate Drive                                                        |  |  |  |

| PG    | 8        | Output | Output CMOS Open Drain - Power Good, indicates external FET fully on |  |  |  |

#### **Overview**

The SLG55021 N-Channel FET Gate Driver is used for controlling a delayed turn on and ramping slew rate of the source voltage on N-Channel FET switches from a CMOS logic level input. Intended as a supporting control element for switched voltage rails in energy efficient, advanced power management systems, the SLG55021 also integrates circuits to discharge opened switched voltage rails. The gate driver is available in a variety of configurations supporting a range of turn-on slew rates from 0.80 V/ms up to 4 V/ms which, depending on load supplying source voltages in the range of 1.0 V to 20 V results in ramp times from 200  $\mu$ s up to over 20 ms (see Application Section). Delays until the ramp begins are source voltage independent and range from 250  $\mu$ s to 5 ms. A power good condition is output to indicate that the ramp-up slew of the source voltage is finished. Additionally, an internal discharge circuit provides a controlled path to remove charge from open power rails. The SLG55021 gate drive is packaged in an 8 pin DFN package.

When used with external N-Channel FETs, the SLG55021 supports low transient, energy efficient switching of high current loads at source voltages ranging from 1.0 V to 20 V.

# **Ordering Information**

| Part Number        | Ramp Slew<br>Rate<br>(Volts/ms) | Delay Time<br>(ms) | Discharge<br>Resistor<br>(ohms) | Package Type                      |

|--------------------|---------------------------------|--------------------|---------------------------------|-----------------------------------|

| SLG55021-200010V   | 2.0                             | 0.15               | 200                             | TDFN-8                            |

| SLG55021-200010VTR | 2.0                             | 0.15               | 200                             | TDFN-8 - Tape and Reel (3k units) |

# **Absolute Maximum Ratings**

| Parameter                               | Min. | Max. | Unit |

|-----------------------------------------|------|------|------|

| V <sub>D</sub> or V <sub>S</sub> to GND | -0.3 | 40.0 | V    |

| Voltage at Logic Input pins             | -0.3 | 6.5  | V    |

| Current at input pin                    | -1.0 | 1.0  | mA   |

| Storage temperature range               | -65  | 150  | °C   |

| Operating temperature range             | -55  | 125  | °C   |

| Junction temperature                    |      | 150  | °C   |

| ESD Human Body Model                    |      | 2000 | V    |

| ESD Machine Model                       |      | 200  | V    |

| Moisture Sensitivity Level              |      | 1    |      |

# **Electrical Characteristics**

$T_A = -10 \, ^{\circ}\text{C}$  to 75  $^{\circ}\text{C}$

| Parameter              | Description                 | Conditions                                     | Min.  | Тур. | Max.  | Unit |

|------------------------|-----------------------------|------------------------------------------------|-------|------|-------|------|

| V <sub>CC</sub>        | Supply Voltage              |                                                | 4.75  | 5.0  | 5.25  | V    |

|                        | Quiescent Current           | V <sub>G</sub> not ramping<br>FET = ON         |       | <7   | 10    | μА   |

| l <sub>q</sub>         | Quiescent Current           | V <sub>G</sub> not ramping<br>FET = OFF        |       | 0.1  | 1     | μА   |

| V <sub>D</sub>         | FET Drain Voltage           | SLG55021                                       | 1.0   |      | 20    | V    |

| V <sub>GS</sub>        | Gate-Source Voltage         | SLG55021                                       | 8.0   | 11.5 | 13    | V    |

| C <sub>G</sub>         | FET Gate Capacitance        |                                                | 500   |      | 8000  | pF   |

| T <sub>DELAY</sub>     | Ramp Delay Range            | 1.5ms Default, 500μs step                      | 0.105 | 0.15 | 0.195 | ms   |

| T <sub>SLEW</sub>      | FET Turn on Slew Rate       |                                                | 1.4   | 2.0  | 2.6   | V/ms |

| I <sub>DISCHARGE</sub> | Internal Discharge Resistor | Nominal discharge time of ~100ms 10mA max rate | 100   | 200  | 300   | Ω    |

| V <sub>IH</sub>        | HIGH-level input voltage    | ON, SHDN#<br>(200mV Hysteresis)                | 2.4   |      | 5.5   | V    |

| V <sub>IL</sub>        | LOW-level Input voltage     | ON, SHDN#<br>(200mV Hysteresis)                |       |      | 0.4   | V    |

| V <sub>OH</sub>        | HIGH-level output voltage   | PG Open Drain                                  |       |      | 5.5   | V    |

| I <sub>OL_LOGIC</sub>  | Logic LOW level output      | PG Sink Current                                | 1     | 2    | 3     | mA   |

| I <sub>IH</sub> *      | SHDN#                       | V <sub>IH</sub> = 3.3V                         |       |      | <1.0  | μΑ   |

| I <sub>G_OL</sub>      | Gate Drive Sink Current     |                                                | 400   |      |       | μΑ   |

| I <sub>G_OH</sub>      | Gate Drive Source Current   |                                                | 32    |      |       | μΑ   |

| I <sub>D_IH</sub>      | Drain Pin Current           | V <sub>D</sub> = 20V in Standby                |       |      | <1.0  | μΑ   |

| I <sub>S_IH</sub>      | Source Pin Current Quiesent | V <sub>S</sub> = 20V                           |       |      | <1.0  | μА   |

| Notes:                 |                             | ·                                              | •     | •    | •     |      |

Notes

1. If using an open drain to drive SHDN#; pull up with 10  $k\Omega$  to  $V_{CC}$

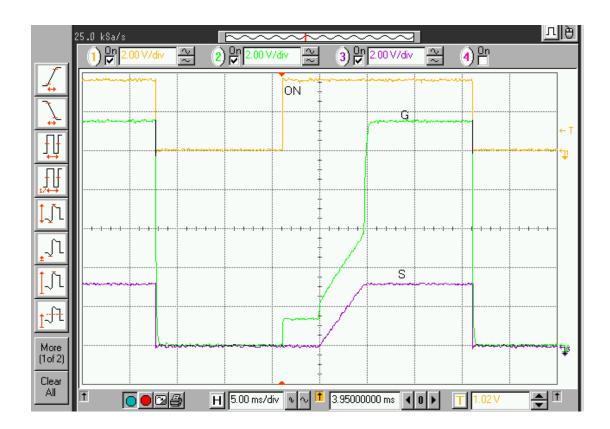

# **Application Example**

In a typical application, de-asserting ON (low) or asserting the low true Shut Down signal (SHDN#) turns off the external power N-FET. SHDN# is provided as an asynchronous override to the ON signal. When the FET is turned off, the voltage at the load is discharged through a resistor (typically 200 ohms) internal to the SLG55021 with the discharge current limited to a maximum of 10mA. When ON is asserted (high), gate voltage is not applied to the gate of the external power N-FET until after T<sub>DELAY</sub> then the gate source (Vgs) voltage is ramped up to 11.5 V above the source voltage V<sub>S</sub> at a slew rate determined by the internal slew rate control element internal to the SLG55021. Monotonic rise of Vs is maintained even as ID increases dramatically after the load device turn on threshold voltage is reached. After the source voltage has ramped up to its maximum steady state value, the Open Drain PG (Power Good) signal is asserted. PG may be used as the ON control of a second SLG55021 thereby providing power on sequence control of a number of switched power rails, or used in a 'wired and' with other PG signals to indicate all switched power rails are in a power good condition.

The devices will not operate if Vcc is below 3.5 V.

The waveforms shown illustrate the monotonic rise of the source voltage of a FET as gate voltage is controlled to accommodate for variations in load current as the voltage is applied.

# Package Top Marking System Definition For devices manufactured after 2021

| PPP       | Part Code                           |

|-----------|-------------------------------------|

| NNN       | Serial Number                       |

| $\circ$ R | Pin 1 Identifier +<br>Revision Code |

PPP - Part Code Field: Identifies the specific device Configuration

NNN - Serial Number Field: Serial number R - Revision Code Field: Device Revision

### For devices manufactured before 2021

| XXA       | Part ID +<br>Assembly Code          |

|-----------|-------------------------------------|

| DDL       | Date Code +<br>Lot                  |

| $\circ$ R | Pin 1 Identifier +<br>Revision Code |

XX - Part ID Field: Identifies the specific device Configuration

A - Assembly Code Field: Assembly Location of the device

DD - Date Code Field: Coded Date of Manufacture

L - Lot Code: Designates Lot #

R - Revision Code: Device Revision

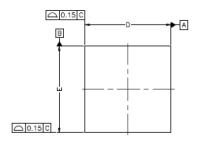

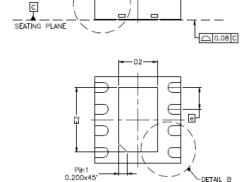

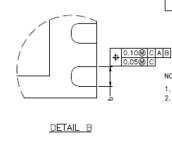

# **Package Drawing and Dimensions**

## 8 Lead TDFN Package

// 0.10 C

|        |      | IMENSION | V    | DIMENSION |      |      |  |

|--------|------|----------|------|-----------|------|------|--|

| SYMBOL |      | (MM)     |      | (MIL)     |      |      |  |

|        | MIN. | NOM.     | MAX. | MIN.      | NOM. | MAX. |  |

| Α      | 0.70 | 0.75     | 0.80 | 28        | 30   | 31   |  |

| A1     | 0.00 | 0.02     | 0.05 | 0         | 1    | 2    |  |

| A2     | 0    | 0.55     | 0.80 | 0         | 22   | 31   |  |

| A3     | _    | 0.20     | -    | _         | 8    | _    |  |

| b      | 0.18 | 0.25     | 0.30 | 7         | 10   | 12   |  |

| D      | 1.90 | 2.00     | 2.10 | 74        | 79   | 83   |  |

| D1     |      | -        |      | _         |      |      |  |

| D2     | 0.75 | 0.90     | 1.05 | 30        | 35   | 41   |  |

| E      | 1.90 | 2.00     | 2.10 | 75        | 79   | 83   |  |

| E1     |      | _        |      |           | _    |      |  |

| E2     | 1.50 | 1.65     | 1.70 | 53        | 59   | 65   |  |

| е      | (    | 0.50 BSC | ;    | 20 BSC    |      |      |  |

| L      | 0.25 | 0.30     | 0.35 | 10        | 12   | 14   |  |

- 1. REFER TO JEDEC STD: MO-229.

2. DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15MM AND 0.30MM FROM THE TERMINAL TIP. IF THE TERMINAL HAS OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION B SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

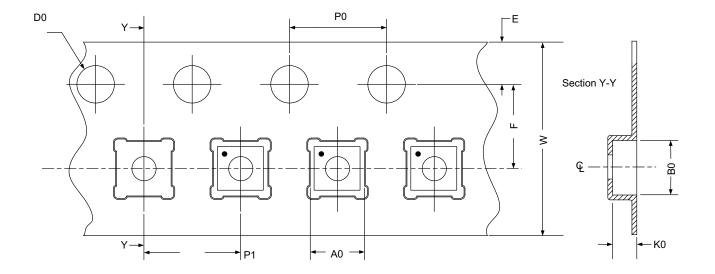

# **Tape and Reel Specifications**

| Dookogo          | #            | Nominal Max Units    |          | Units   | Reel &                | Leader (min) |                | Trailer (min) |                | Tape          | Part          |

|------------------|--------------|----------------------|----------|---------|-----------------------|--------------|----------------|---------------|----------------|---------------|---------------|

|                  | # of<br>Pins | Package Size<br>[mm] | per Reel | per Box | per Box Hub Size [mm] | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| TDFN 8L<br>Green | 8            | 2 x 2 x 0.75         | 3,000    | 3,000   | 178 / 60              | 100          | 400            | 100           | 400            | 8             | 4             |

# **Carrier Tape Drawing and Dimensions**

| Package<br>Type  | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge | Index Hole<br>to Pocket<br>Center | Tape Width |

|------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|-----------------------------------|------------|

|                  | A0                  | В0                 | K0              | P0                  | P1              | D0                     | E                             | F                                 | W          |

| TDFN 8L<br>Green | 2.3                 | 2.3                | 1.05            | 4                   | 4               | 1.55                   | 1.75                          | 3.5                               | 8          |

# **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 3.00 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

# **Revision History**

| Date      | Version | Change                                                  |  |  |  |

|-----------|---------|---------------------------------------------------------|--|--|--|

| 6/7/2023  | 1.06    | Updated Part Marking Definition                         |  |  |  |

| 2/9/2022  | 1.05    | Ipdated Company name and logo<br>iixed typos            |  |  |  |

| 7/10/2018 | 1.04    | pdated style and formatting                             |  |  |  |

| 7/27/2017 | 1.03    | Added Pb-Free/Halogen Free/RoHS compliance<br>Added MSL |  |  |  |

| 9/26/2016 | 1.02    | Removed TBD values<br>Fixed typos                       |  |  |  |

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01 Jan 2024)

## **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.